Využívanie vnorených rezistorov v návrhu DPS

18. Február, 2013, Autor článku: Livovský Ľubomír, Elektrotechnika

Ročník 6, číslo 2  Pridať príspevok

Pridať príspevok

![]() Pasívne súčiastky predstavujú veľkú časť dnešných elektronických zariadení. Platí to hlavne pre digitálne zariadenia, ako sú mobilné telefóny, digitálne videokamery a počítače. Tlak trhu na nové výrobky s väčšou integráciou funkcií, menšou veľkosťou a nižšími výrobnými nákladmi si vyžadujú menšie, kompaktnejšie a zložitejšie obvodové riešenia. Medzi hlavné stratégie ako sa prispôsobiť trhu môžeme zaradiť aj znižovanie počtu pasívnych SMD (Surface Mount Devices) súčiastok montovaných na povrchu substrátov, ktoré je možné vložiť do vnútra substrátu resp. DPS (Dosky plošných Spojov).

Pasívne súčiastky predstavujú veľkú časť dnešných elektronických zariadení. Platí to hlavne pre digitálne zariadenia, ako sú mobilné telefóny, digitálne videokamery a počítače. Tlak trhu na nové výrobky s väčšou integráciou funkcií, menšou veľkosťou a nižšími výrobnými nákladmi si vyžadujú menšie, kompaktnejšie a zložitejšie obvodové riešenia. Medzi hlavné stratégie ako sa prispôsobiť trhu môžeme zaradiť aj znižovanie počtu pasívnych SMD (Surface Mount Devices) súčiastok montovaných na povrchu substrátov, ktoré je možné vložiť do vnútra substrátu resp. DPS (Dosky plošných Spojov).

Úvod

Aktuálne prepojovacie technológie povrchovo montovaných súčiastok už predstavujú určité obmedzenia v návrhu topológie dosiek plošných spojov, ktoré sa podieľajú na znížení celkovej rýchlosti obvodov. Technológia vnorených pasívnych súčiastok je jednou z možností, ako zmenšovať rozmery substrátov a tým aj náklady na výrobu, ako aj podstatné zníženie parazitných účinkov a zlepšenie celkového výkonu elektronických obvodov.

Vnorené pasívne súčiastky

Z troch typov pasívnych súčiastok ako sú rezistory, kondenzátory a cievky, hlavne rezistory a kondenzátory poskytujú potenciálny prínos pre obvody s vysokou hustotou, vysokou rýchlosťou. Pasívne súčiastky môžu byť vnorené v prepojovacom substráte (DPS, Multi-Chip Module – Laminated) za účelom zlepšenia frekvenčných vlastností substrátov. Vnorené rezistory sú veľkým prínosom pri vytváraní „Pull-up“, „Pull-down“ rezistorov, ktoré zabezpečujú definovaný potenciál na vstupoch resp. výstupoch obvodov alebo ukončovací odpor za účelom impedančného prispôsobenia vývodov. Vnorené kondenzátory sa využívajú hlavne vo funkcii blokovacích kondenzátorov používaných k oddeleniu častí elektronického obvodu. Vnorené cievky sa využívajú hlavne v DC-DC meničoch, resp. v obvodoch napájania elektronických modulov [2].

Vnorené rezistory a kondezátory sa vytvárajú zo špeciálnych materiálov, ktoré sa vkladajú medzi vrstvy viacvrstvovej DPS. Tieto materiály sú vo všeobecnosti veľmi tenké, aby sa nezväčšovala hrúbka výslednej DPS. Oproti tomu sa vnorené cievky vytvárajú prevažne vo forme plošných cievok na jednotlivých vrstvách DPS. Jednotlivé časti výslednej cievky sú prepojené pomocou prekovených otvorov „Blind Vias“ len v tých vrstvách, v ktorých je cievka vytvorená.

Materiál pre vnorené rezistory

Vytvorenie vnorených rezistorov je podmienené použitím odporového materiálu , ktorý je možné laminovať do výslednej zostavy DPS. Materiál musí vyhovovať technológii výroby viacvrstvovej DPS, čím sa proces výroby DPS rozšíri. Jednou z možností ako vytvoriť vnorený rezistor je použitie materiálu na báze nikel-fosforovej (NiP) zliatiny, ktorá má vyhovujúce ohmické vlastnosti, vykazuje vysokú stabilitu hodnôt odporu a vyhovuje procesu technológie výroby DPS a taktiež procesu spájkovania súčiastok bezolovnatou spájkou.

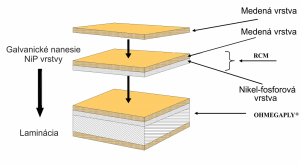

Materiál na báze nikel-fosforovej zliatiny „OhmegaPly“ ponúka riešenie vnorených rezistorov. Odporová nikel-fosforová zliatina je elektrochemicky nanesená na vodivú medenú vrstvu, čím sa vytvorí zostava vo forme tenkej odporovo-vodivej vrstvy označovanej aj ako RCM (Resistor-Conductor Material). Tento materiál je potom laminovaný s dielektrickým materiálom (epoxidovým, polyimidovým, PTFEs), čím sa vytvorí štandardná doska plošného spoja s vnútornou odporovou vrstvou zobrazená na obrázku Obr.1. Týmto spôsobom je možné vytvoriť napríklad dvojstrannú DPS na báze FR4 s dvoma medenými (vodivými) vrstvami a jednou NiP odporovou vrstvou [1].

Obr. 1: Znázornenie výroby RCM materiálu.

Na takto vytvorenej DPS sa pomocou procesu leptania vytvárajú požadované rezistory. Podľa hrúbky NiP vrstvy je možné vytvárať odporovo-vodivý materiál (RCM) s rôznymi hodnotami plošného odporu. Bežne dostupné hodnoty a ich použitie je uvedené v tabuľke Tab.1.

Tab. 1: Rôzne hodnoty plošných odporov NiP odporovej vrstvy.

| Plošný odpor Rs | Tolerancia | Hrúbka NiP | Aplikácia, použitie |

|---|---|---|---|

| 10 Ω/□ | 3% | 1.00 um | Sériové ukončovacie rezistory, ktoré sú súčasťou vodivej čiary. |

| 25 Ω/□ | 5% | 0.40 um | Použiteľné pre sériové a paralelné ukončovacie rezistory a výkonové odporové deliče. |

| 50 Ω/□ | 5% | 0.20 um | |

| 100 Ω/□ | 5% | 0.10 um | Použitie ako „Pull-up“ , „Pull-down“ rezistory pre logické obvody |

| 250 Ω/□ | 10% | 0.05 um | Rezistory s veľkou hodnotou odporu |

Návrh odporu rezistora

Plošný odpor (Rs – odpor na jednotku plochy) nezávisí na rozmeroch pri zachovaní rovnosti strán rezistora. Pri návrhu rozmerov a tvaru požadovaného rezistora sa vychádza z hodnoty plošného odporu použitej NiP vrstvy. Hodnota odporu rezistora v tvare obdĺžnika sa potom vypočíta podľa vzťahu:

| (1) |

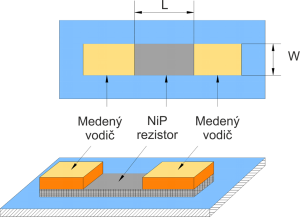

kde R je požadovaná hodnota rezistora, Rs – odpor na jednotku plochu, L – dĺžka rezistora, W – šírka rezistora (Obr. 2).

Obr. 2: Zobrazenie RCM rezistora

Výsledný rezistor nemusí mať len tvar obdĺžnika (čiary), ale môže byť aj v tvare meandra za účelom šetrenia miesta alebo vytvorenie plošného odporového ohrievača. Možnosti návrhu sú zobrazené v nasledujúcich obrázkoch. Pre výpočet odporu na obrázku Obr.3 platí hore uvedený vzťah, ale pre výpočet meandrového odporu je potrebné použiť nasledujúcu úvahu.

Obr. 3: Návrh RCM rezistora v tvare obdĺžnika.

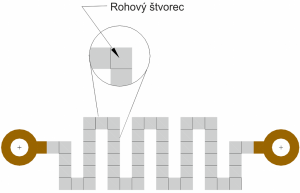

Rezistor meandrového typu pozostáva z niekoľkých plošných rezistorov, ktoré sú navzájom prepojené v pravom uhle pomocou „rohových“ rezistorov. Z dôvodu zmeny prúdovej hustoty v rohových segmentoch meandra sa mení ich efektívny odpor z hodnoty 1 na hodnotu 0,56. Výpočet odporu meandra na obrázku Obr. 4 je nasledovný: Ak použitý materiál má hodnotu plošného odporu Rs = 100 Ω/□ , počet štvorcov meandra je 37, počet rohových rezistorov je 16, potom počet efektívnych štvorcových rezistorov, ktoré sa podieľajú na výslednej hodnote odporu je 37 + (16 x 0,56) = 45,9. Výsledná hodnota odporu meandra bude približne: 46 x 100 = 4,6 K Ω. (Na výslednú hodnotu odporu má aj vplyv kvalita leptania medi resp. nikel-fosforovej vrstvy – podleptanie).

Obr. 4: Návrh RCM rezistora v tvare meandra.

Technológia výroby vnorených rezistorov

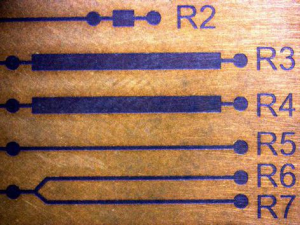

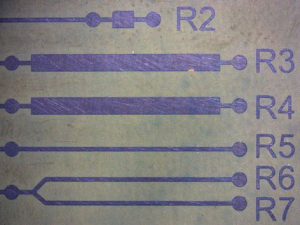

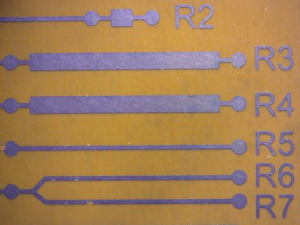

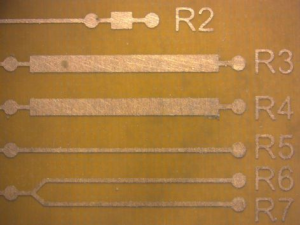

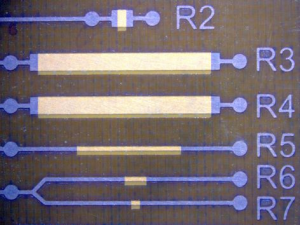

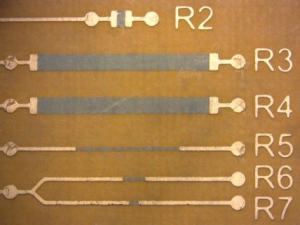

Technologický proces výroby vnorených rezistorov pozostáva z nasledujúcich krokov [1], ktoré sú prezentované na vzorke odporov vyrobených na RCM materiály s hodnotou Rs = 25 Ω/□:

- rezistor R2 s nominálnou hodnotou 12,5 Ω je polovičný štvorcový rezistor,

- rezistory R3, R4 s nominálnou hodnotou 250 Ω sú rezistory, ktoré sa skladajú z 10 štvorcových rezistorov,

- rezistory R5, R6, R7 predstavujú sériové ukončovacie rezistory. R5 s nominálnou hodnotou 600 Ω je vytvorený z 25 štvorcových rezistorov, R6 s nominálnou hodnotou 125 Ω je vytvorený 5 štvorcovými rezistorov, R7 s nominálnou hodnotou 50 Ω sa skladá z 2 štvorcových rezistorov.

V prvom kroku je potrebné naniesť fotocitlivú emulziu (fotorezist) na vrstvu medi, pod ktorou sa nachádza odporová vrstva. Po osvetlení filmovej predlohy na fotocitlivú vrstvu je potrebné fotocitlivú vrstvu vyvolať, čím sa na medenej vrstve vytvorí obrazec.

V druhom kroku je potrebné odhalenú medenú vrstvu vyleptať pomocou bežného leptacieho procesu buď chloridom železitým alebo kyselinou chlorovodíkovou. Tento proces odstráni meď a odhalí (sivú) nikel-fosforovú odporovú vrstvu.

V treťom kroku je potrebné odleptať odporovú vrstvu, ktorá má podľa použitého RCM hrúbku 0,40 um. Vhodné je použiť leptací roztok, ktorý sa skladá z 250 g/l pentahydrátu síranu meďnatého a 3-5 ml koncentrovanej kyseliny sírovej na 1 liter. Leptanie by malo trvať 3-15 minút v závislosti od veľkosti leptanej plochy a kvality leptacieho roztoku.

Po odleptaní odporovej vrstvy je potrebné odstrániť fotocitlivú vrstvu napríklad pomocou acetónu, hydroxidu sódneho NaOH alebo hydroxidu draselným KOH. Na obrázku je vidieť medenú vrstvu. Odstránením časti medenej vrstvy sa odhalí odporová vrstva, čím sa vytvoria vnorené rezistory.

Opätovne sa na očistený povrch nanesie fotorezist a osvetlí sa filmová predloha pre odstránenie časti medi, ktorá odkryje odporovú vrstvu. Leptanie v tejto fáze je veľmi kritické, pretože môže dôjsť k podleptávaniu odporovej vrstvy a tým k zmene hrúbky odporovej vrstvy, čo sa prejaví v zmene hodnoty plošného odporu.

Posledný krok je odstránenie fotorezistu z povrchu medenej fólie. Odhalená odporová vrstva je veľmi náchylná na zmenu plošného odporu vplyvom nečistôt, preto je žiaduce s vyrobeným materiálom pokračovať vo výrobe výslednej viacvrstvovej DPS alebo ich hermeticky uskladniť, čím sa zabráni kontaminovaniu a oxidácii povrchu.

Výhody používania vnorených rezistorov

Zakomponovanie vnorených rezistorov do návrhu dosiek plošných spojov prináša so sebou nasledujúce výhody:

- elektrických parametrov: skracovanie signálových ciest a tým redukcia sériovej induktancie, eliminuje sa induktívna reaktancia súčiastok pre povrchovú montáž, redukujú sa presluchy medzi signálmi, šum a celkovo sa zvyšuje elektromagnetická kompatibilita osadenej DPS.

- parametrov návrhu DPS: zvyšovanie hustoty súčiastok na DPS, zmenšovanie počtu prekovených otvorov a tým zväčšenie hustoty prepojovacích vodičov, zmenšenie počtu spájkovaných vývodov súčiastok (vnorené súčiastky sa nespájkujú) a teda celkové zvýšenie spoľahlivosti v oblasti spájkovania.

- ekonomických ukazovateľov: znižovanie počtu diskrétnych súčiastok má za následok zmenšenie počtu osadzovaných súčiastok, šetrenie spájkovacieho materiálu, zrýchlenie výroby elektronických modulov, zmenšovanie rozmerov a tým aj hmotnosti DPS.

Poďakovanie

Podporujeme výskumné aktivity na Slovensku/ Projekt je spolufinancovaný zo zdrojov EÚ. Tento článok bol vypracovaný v rámci projektu “Centrum excelentnosti integrovaného výskumu a využitia progresívnych materiálov a technológií v oblasti automobilovej elektroniky”, ITMS 26220120055.

Podporujeme výskumné aktivity na Slovensku/ Projekt je spolufinancovaný zo zdrojov EÚ. Tento článok bol vypracovaný v rámci projektu “Centrum excelentnosti integrovaného výskumu a využitia progresívnych materiálov a technológií v oblasti automobilovej elektroniky”, ITMS 26220120055.

Literatúra

- Internetový zdroj

www.ohmega.com - R. N. Das, K. I. Papathomas, J. M. Lauffer, S. Rosser, M. D. Poliks and V. R. Markovich: Manufacturing Substrates with Embedded Passives, The PCB Magazin, November 2011, str. 11-15.

- Daniel Brandler: The Performance of Embedded Resistors by Alloy Type and Film Thickness, The PCB Magazin, November 2011 str. 20-29.

- Weiyang Qiu, Kailin Pan, Dongmei li, Jing Liu: Study on Process of Embedded Passives Based on FR4 Substrate Series, 2010 11th International Conference on Electronic Packaging Technology & High Density Packaging, str. 815-818.

Katedra technológií v elektronike, Fakulta elektroniky a informatiky, Technická univerzita v Košiciach